Saps com resoldre el problema EMI quan es dissenya PCB multicapa?

Deixa'm dir-te!

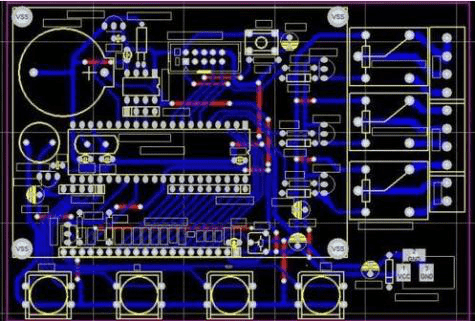

Hi ha moltes maneres de resoldre problemes d'EMI.Els mètodes moderns de supressió d'EMI inclouen: utilitzar el recobriment de supressió EMI, seleccionar peces de supressió EMI adequades i disseny de simulació EMI.A partir del disseny de PCB més bàsic, aquest article tracta la funció de la pila de PCB en el control de la radiació EMI i les habilitats de disseny de PCB.

bus elèctric

El salt de tensió de sortida de l'IC es pot accelerar col·locant la capacitat adequada a prop del pin d'alimentació de l'IC.Tanmateix, aquest no és el final del problema.A causa de la resposta de freqüència limitada del condensador, és impossible que el condensador generi la potència harmònica necessària per conduir la sortida IC de manera neta a la banda de freqüència completa.A més, la tensió transitòria formada al bus d'alimentació provocarà una caiguda de tensió als dos extrems de la inductància del camí de desacoblament.Aquests voltatges transitoris són les principals fonts d'interferència EMI en mode comú.Com podem resoldre aquests problemes?

En el cas de l'IC a la nostra placa de circuit, la capa de potència al voltant de l'IC es pot considerar un bon condensador d'alta freqüència, que pot recollir l'energia filtrada pel condensador discret que proporciona energia d'alta freqüència per a una sortida neta.A més, la inductància d'una bona capa de potència és petita, de manera que el senyal transitori sintetitzat per l'inductor també és petit, reduint així l'EMI en mode comú.

Per descomptat, la connexió entre la capa d'alimentació i el pin de la font d'alimentació IC ha de ser tan curta com sigui possible, perquè la vora ascendent del senyal digital és cada cop més ràpida.És millor connectar-lo directament al coixinet on es troba el pin d'alimentació IC, que s'ha de parlar per separat.

Per controlar l'EMI en mode comú, la capa de potència ha de ser un parell de capes de potència ben dissenyades per ajudar a desacoblar-se i tenir una inductància prou baixa.Algunes persones poden preguntar, què tan bo és?La resposta depèn de la capa de potència, el material entre les capes i la freqüència de funcionament (és a dir, una funció del temps de pujada de l'IC).En general, l'espaiat de les capes de potència és de 6 mil i la capa intermedia és de material FR4, de manera que la capacitat equivalent per polzada quadrada de capa de potència és d'uns 75 pF.Òbviament, com més petit sigui l'espaiat entre capes, més gran serà la capacitat.

No hi ha molts dispositius amb un temps de pujada de 100-300ps, però d'acord amb la taxa de desenvolupament actual d'IC, els dispositius amb un temps de pujada en el rang de 100-300ps ocuparan una proporció elevada.Per a circuits amb temps de pujada de 100 a 300 PS, l'espaiat entre capes de 3 mil ja no és aplicable a la majoria d'aplicacions.En aquest moment, cal adoptar la tecnologia de delaminació amb l'espai entre capes inferior a 1 mil i substituir el material dielèctric FR4 amb el material amb una constant dielèctrica elevada.Ara, la ceràmica i els plàstics en test poden complir els requisits de disseny de circuits de temps de pujada de 100 a 300ps.

Encara que es poden utilitzar nous materials i mètodes en el futur, els circuits de temps de pujada comuns d'1 a 3 ns, l'espaiat entre capes de 3 a 6 mil i els materials dielèctrics FR4 solen ser suficients per gestionar els harmònics de gamma alta i fer que els senyals transitoris siguin prou baixos, és a dir , l'EMI en mode comú es pot reduir molt baix.En aquest document, es dóna l'exemple de disseny d'apilament en capes de PCB i se suposa que l'espai entre capes és de 3 a 6 mil.

blindatge electromagnètic

Des del punt de vista de l'encaminament del senyal, una bona estratègia de capes hauria de ser col·locar totes les traces del senyal en una o més capes, que es troben al costat de la capa de potència o el pla de terra.Per a la font d'alimentació, una bona estratègia de capes hauria de ser que la capa d'alimentació estigui adjacent al pla de terra i la distància entre la capa d'alimentació i el pla de terra hauria de ser el més petita possible, que és el que anomenem estratègia de "capa".

Pila de PCB

Quin tipus d'estratègia d'apilament pot ajudar a protegir i suprimir EMI?El següent esquema d'apilament en capes suposa que el corrent de la font d'alimentació flueix en una sola capa i que una sola o diverses tensions es distribueixen en diferents parts de la mateixa capa.El cas de múltiples capes de potència es comentarà més endavant.

Placa de 4 capes

Hi ha alguns problemes potencials en el disseny de laminats de 4 capes.En primer lloc, fins i tot si la capa de senyal es troba a la capa exterior i el pla de potència i terra es troben a la capa interior, la distància entre la capa de potència i el pla de terra encara és massa gran.

Si el requisit de cost és el primer, es poden considerar les dues alternatives següents al tauler tradicional de 4 capes.Tots dos poden millorar el rendiment de la supressió EMI, però només són adequats per al cas en què la densitat dels components a la placa sigui prou baixa i hi hagi prou àrea al voltant dels components (per col·locar el recobriment de coure necessari per a l'alimentació).

El primer és l'esquema preferit.Les capes exteriors de PCB són totes capes, i les dues capes centrals són capes de senyal / potència.La font d'alimentació de la capa de senyal s'encamina amb línies amples, cosa que fa que la impedància del camí del corrent de la font d'alimentació sigui baixa i la impedància del camí de la microstrip del senyal sigui baixa.Des de la perspectiva del control EMI, aquesta és la millor estructura de PCB de 4 capes disponible.En el segon esquema, la capa exterior transporta la potència i la terra, i la capa central dos porta el senyal.En comparació amb la placa tradicional de 4 capes, la millora d'aquest esquema és més petita i la impedància entre capes no és tan bona com la de la placa tradicional de 4 capes.

Si s'ha de controlar la impedància del cablejat, l'esquema d'apilament anterior hauria de tenir molta cura de posar el cablejat sota l'illa de coure d'alimentació i connexió a terra.A més, l'illa de coure a la font d'alimentació o estrat s'ha d'interconnectar tant com sigui possible per garantir la connectivitat entre DC i baixa freqüència.

Placa de 6 capes

Si la densitat dels components de la placa de 4 capes és gran, la placa de 6 capes és millor.Tanmateix, l'efecte de blindatge d'alguns esquemes d'apilament en el disseny de la placa de 6 capes no és prou bo i el senyal transitori del bus d'alimentació no es redueix.A continuació es comenten dos exemples.

En el primer cas, la font d'alimentació i la terra es col·loquen a la segona i la cinquena capes respectivament.A causa de l'alta impedància de la font d'alimentació revestida de coure, és molt desfavorable controlar la radiació EMI en mode comú.Tanmateix, des del punt de vista del control de la impedància del senyal, aquest mètode és molt correcte.

En el segon exemple, la font d'alimentació i la terra es col·loquen a la tercera i quarta capes respectivament.Aquest disseny resol el problema de la impedància revestida de coure de la font d'alimentació.A causa del mal rendiment de blindatge electromagnètic de la capa 1 i la capa 6, augmenta el mode diferencial EMI.Si el nombre de línies de senyal a les dues capes exteriors és el mínim i la longitud de les línies és molt curta (menys d'1/20 de la longitud d'ona harmònica més alta del senyal), el disseny pot resoldre el problema del mode diferencial EMI.Els resultats mostren que la supressió de l'EMI en mode diferencial és especialment bona quan la capa exterior s'omple de coure i l'àrea revestida de coure es posa a terra (cada interval de longitud d'ona 1/20).Com s'ha esmentat anteriorment, s'ha de posar coure

Hora de publicació: 29-jul-2020